have one or more of the following advantages: higher input-output isolation, higher input impedance, higher output impedance, higher gain or higher bandwidth. In modern

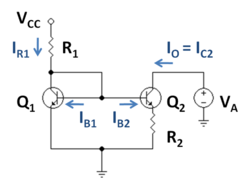

circuits, the cascode is often constructed from two transistors (BJTs or FETs), with one operating as a common emitter or common source and the other as a common base

or common gate. The cascode improves input-output isolation (or reverse transmission) as there is no direct coupling from the output to input. This eliminates the Miller

effect and thus contributes to a much higher bandwidth.

History:

The cascode (sometimes verbified to cascoding) is a universal technique for improving analog circuit performance, applicable to both vacuum tubes and transistors. The

word "cascode" is a contraction of the phrase "cascade to cathode". It was first used in an article by F.V. Hunt and R.W. Hickman in 1939, in a discussion for application

in low-voltage stabilizers.[1] They proposed a cascode of two triodes (first one with common cathode, the second one with common grid) as a replacement of a pentode.

Operation:

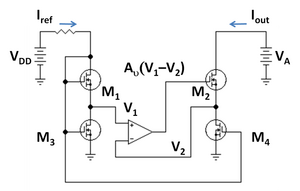

The major advantage of this circuit arrangement stems from the placement of the upper Field Effect Transistor (FET) as the load of the input (lower) FET's output

terminal (drain). Because at operating frequencies the upper FET's gate is effectively grounded, the upper FET's source voltage (and therefore the input transistor's

drain) is held at nearly constant voltage during operation. In other words, the upper FET exhibits a low input resistance to the lower FET, making the voltage gain of the

lower FET very small, which dramatically reduces the Miller feedback capacitance from the lower FET's drain to gate. This loss of voltage gain is recovered by the upper

FET. Thus, the upper transistor permits the lower FET to operate with minimum negative (Miller) feedback, improving its bandwidth.

The upper FET gate is electrically grounded, so charge and discharge of stray capacitance Cdg between drain and gate is simply through RD and the output load (say Rout),

and the frequency response is affected only for frequencies above the associated RC time constant: τ = Cdg RD//Rout, namely f = 1/(2πτ), a rather high frequency because

Cdg is small. That is, the upper FET gate does not suffer from Miller amplification of Cdg.

If the upper FET stage were operated alone using its source as input node (i.e. common-gate (CG) configuration), it would have good voltage gain and wide bandwidth.

However, its low input impedance would limit its usefulness to very low impedance voltage drivers. Adding the lower FET results in a high input impedance, allowing the

cascode stage to be driven by a high impedance source.

If one were to replace the upper FET with a typical inductive/resistive load, and take the output from the input transistor's drain (i.e. a common-emitter (CE)

configuration), the CE configuration would offer the same input impedance as the cascode, but the cascode configuration would offer a potentially greater gain and much

greater bandwidth.

Stability:

The cascode arrangement is also very stable. Its output is effectively isolated from the input both electrically and physically. The lower transistor has nearly constant

voltage at both drain and source and thus there is essentially "nothing" to feed back into its gate. The upper transistor has nearly constant voltage at its gate and source.

Thus, the only nodes with significant voltage on them are the input and output, and these are separated by the central connection of nearly constant voltage and by the

physical distance of two transistors. Thus in practice there is little feedback from the output to the input. Metal shielding is both effective and easy to provide between

the two transistors for even greater isolation when required. This would be difficult in one-transistor amplifier circuits, which at high frequencies would require

neutralization.

Biasing:

As shown, the cascode circuit using two "stacked" FET's imposes some restrictions on the two FET's-namely, the upper FET must be biased so its source voltage is high

enough (the lower FET drain voltage may swing too low, causing it to leave saturation). Insurance of this condition for FET's requires careful selection for the pair, or

special biasing of the upper FET gate, increasing cost.

The cascode circuit can also be built using bipolar transistors, or MOSFETs, or even one FET (or MOSFET) and one BJT. In the latter case, the BJT must be the upper

transistor; otherwise, the (lower) BJT will always saturate (unless extraordinary steps are taken to bias it).

Advantages:

The cascode arrangement offers high gain, high slew rate, high stability, and high input impedance. The parts count is very low for a two-transistor circuit.

Disadvantages:

The cascode circuit requires two transistors and requires a relatively high supply voltage. For the two-FET cascode, both transistors must be biased with ample VDS in

operation, imposing a lower limit on the supply voltage.

Dual-gate version:

A dual-gate MOSFET often functions as a "one-transistor" cascode. Common in the front ends of sensitive VHF receivers, a dual-gate MOSFET is operated as a common-

source amplifier with the primary gate (usually designated "gate 1" by MOSFET manufacturers) connected to the input and the 2nd gate grounded (bypassed). Internally,

there is one channel covered by the two adjacent gates; therefore, the resulting circuit is electrically a cascode composed of two FETs, the common lower-drain-to-upper-

source connection merely being that portion of the single channel that lies physically adjacent to the border between the two gates.

Figure 1: N-channel cascode amplifier with resistive load (neglecting biasing details)

Obtenido de: http://en.wikipedia.org/wiki/Cascode